- Available Rules

- Run in Batch Mode

- Run in GUI Mode

- Compile Arguments

- Auto-config

- Emulating compiler invocations

- Compatibility Modes

- Paths

- Strings

- Comments

- Environment Variables

- Including Other Argument Files

- All Build Directives

- SystemVerilog OVM or UVM Library Compilation

- Xilinx Libraries Compilation

- Intel(Altera) Quartus Libraries Compilation

- Questa Libraries Compilation

- Use of External Programs

- HTML Report

- HTML Progress Report

- Custom Report

- > Rulesets

- Lint Waivers

- Compile Waivers

- Report Merging, Diffing and Comparing

- Auto-correct

- API for Writing Custom Rules

- Memory Monitor

- Application Notes

- Q & A

- What is New?

- Legal Notices

- Third Party Licenses

Verissimo can be run either with a custom ruleset or one of the predefined rulesets. The available predefined rulesets are the following:

| Ruleset | Description | Argument |

| All Rules | All the available rules from the rulepool | all |

| Basic Rules | Rules that are a good starting point in the absence of an existing guideline or custom ruleset | basic |

| UVM Compliance Rules | Rules related to UVM architecture compliance | compliance |

| Dead Code Rules | Rules related to dead code detection: empty statements, unused elements, etc. | dead_code |

| Non-Standard Rules | Rules responsible for detecting non-standard constructs or syntax | non_standard |

| Performance Rules | Rules related to issues that can lead to poor simulator performance | performance |

| RTL Rules | Rules related to RTL design issues | rtl |

| UVM IEEE 1800.2-2020 Compliance Rules | Rules that flag the usage of removed, deprecated, non-standard UVM IEEE API. This ruleset is useful in helping with migration to UVM IEEE. | uvm_ieee |

To run the predefined rulesets in batch mode simply use the associated argument (-all, -basic, etc) instead of -ruleset. By default if no -ruleset or no predefined ruleset argument is used, the Basic Rules will be run. In batch mode to generate the ruleset XML file use the -gen_ruleset_xml argument with the corresponding predefined ruleset argument:

verissimo.sh -gen_ruleset_xml -basic

For the associated HTML documentation of a predefined ruleset use the -gen_ruleset_doc argument:

verissimo.sh -gen_ruleset_doc -performance

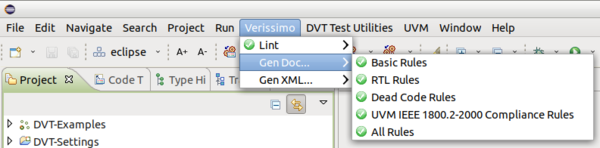

To generate these file from DVT go to the Verissimo menu and go to Generate Doc... or Generate XML and select de desired ruleset.