- Installation

- User Interface

- Predefined Projects

- Build Configurations

- Project Natures

- Non-top files

- default.build

- Auto-config

- Simulator Log-config

- Emulating compiler invocations

- Multiple .build Files

- Compatibility Modes

- Paths

- Strings

- Comments

- Environment Variables

- Including Other Argument Files

- Build Persistence

- All Build Directives

- SystemVerilog OVM or UVM Library Compilation

- Xilinx Libraries Compilation

- Intel(Altera) Quartus Libraries Compilation

- Questa Libraries Compilation

- Use of External Programs

- Compile Checks

- Quick Fix Proposals

- Content Assist (Autocomplete)

- Hyperlinks

- Show Usages

- Show Readers or Writers

- Show Call Hierarchy

- Show Type Hierarchy

- Show Constraints

- Show Instances

- Peek Exploration

- Refactoring

- Override Functions

- Generate Setters and Getters

- Code Factory

- > Code Formatting

- Breadcrumb Navigation Bar

- Diagrams

- Syntax Coloring

- Tooltips

- Workspace Symbols

- Views

- Quick Search in Views

- Content Filters

- Macros Support

- Inactive Generates Code Highlight

- Database Out of Sync Notification

- External Tools Integration

- UVM Support

- Scripts

- Custom Scripts

- SCM Checkout Hook

- Memory Monitor

- Application Notes

- Handy VS Code Documentation Pointers

- What is New?

- How to Report an Issue?

- Legal Notices

- Third Party Licenses

- Q & A

When enabled, this option performs vertical alignment.

Vertical Alignment Tokens (DVT.textEditor.systemVerilog.formatting.verticalAlignment.verticalAlignTokens)

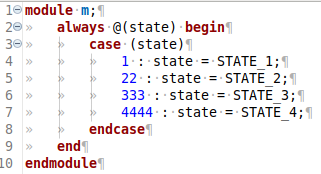

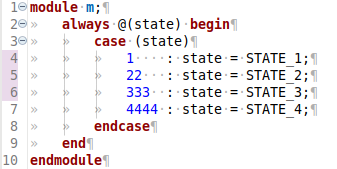

The lines of code inside the same scope are aligned by the specified list of vertical alignment tokens. Vertical alignment is performed left to right, by the same token. For example, assuming '=' and ':' as vertical align tokens: In order to use the comma character ',' as a vertical alignment token, the character must be preceded by the escaping character '\'.

| Before | After (":" token) |

|

|

Only Consecutive Lines (DVT.textEditor.systemVerilog.formatting.verticalAlignment.onlyConsecutiveLines) - Controls whether vertical alignment is applied only to consecutive lines.

| Before | After |

|

|

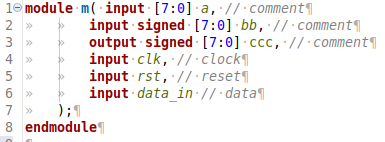

Vertical Align Single Line Comments (DVT.textEditor.systemVerilog.formatting.verticalAlignment.verticalAlignSingleLineComments) - Controls whether single line comments are vertically aligned.

| Before | After |

|

|

Vertical Align To Open Parenthesis (DVT.textEditor.systemVerilog.formatting.verticalAlignment.verticalAlignToOpenParenthesis) - Controls whether to vertically align relative to open parenthesis.

| Before | After |

|

|

Vertical Align To Open Curly (DVT.textEditor.systemVerilog.formatting.verticalAlignment.verticalAlignToOpenCurly) - Controls whether to vertically align relative to open curly.

| Before | After |

|

|

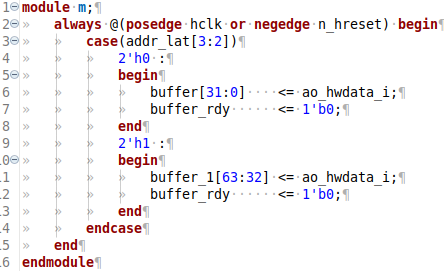

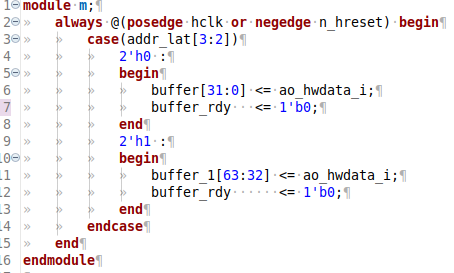

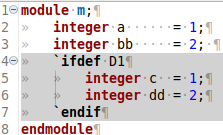

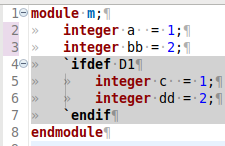

Independent Preprocessing Scopes (DVT.textEditor.systemVerilog.formatting.verticalAlignment.independentPreprocessingScopes) - Controls whether preprocessing scopes create independent alignment scopes.

| Before | After |

|

|

Vertical Align Patterns (DVT.textEditor.systemVerilog.formatting.verticalAlignment.verticalAlignPatterns) :

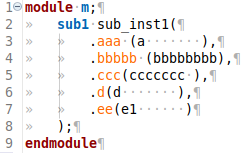

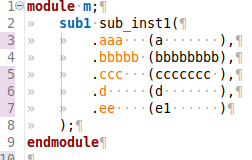

By Name Port Connections (VlogByNamePortConnections) - Controls whether to align instance port connections by name.

| Before | After |

|

|

Class Declarations (VlogClassDeclarations) - Controls whether to align class parameters.

| Before | After |

|

|

Class Variable Declarations (VlogClassVariableDeclarations) - Controls whether to align class variables.

| Before | After |

|

|

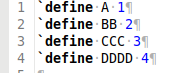

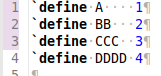

' `defines' (VlogDefines) - Controls whether to align `defines.

| Before | After |

|

|

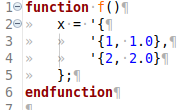

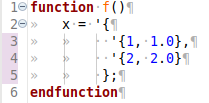

Function Declarations (VlogFunctionDeclarations) - Controls whether to align function and task declarations.

| Before | After |

|

|

Function Variable Declarations (VlogFunctionVariableDeclarations) - Controls whether to align function and task variable declarations.

| Before | After |

|

|

Interface Port Declarations (VlogInterfacePortDeclarations) - Controls whether to align interface ports.

| Before | After |

|

|

Interface Signal Declarations (VlogInterfaceSignalDeclarations) - Controls whether to align interface signals.

| Before | After |

|

|

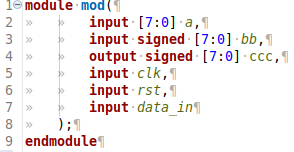

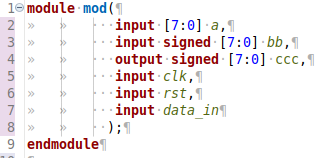

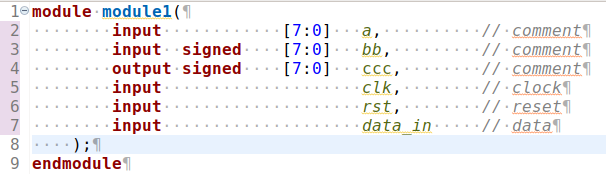

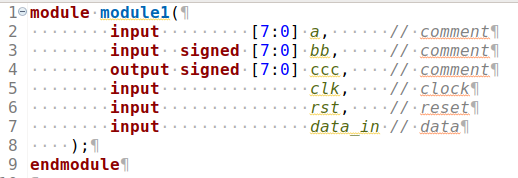

Module Port Declarations (VlogModulePortDeclarations) - Controls whether to align module ports.

| Before | After |

|

|

Module Signal Declarations (VlogModuleSignalDeclarations) - Controls whether to align module signals.

| Before | After |

|

|

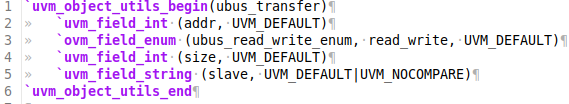

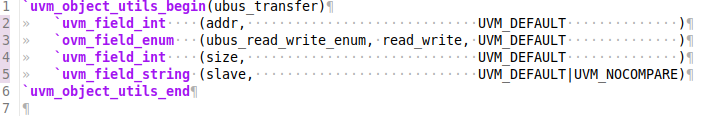

`xvm_field macros (VlogXVMFieldMacros) - Controls whether to align `xvm_field factory registration macros.

| Before | After |

|

|

Compact Whitespace For Vertical Align Patterns (DVT.textEditor.systemVerilog.formatting.verticalAlignment.compactWhitespaceForVerticalAlignPatterns) - Controls whether consecutive whitespace characters are trimmed to a single space character for vertical align patterns.

| Before | After |

|

|